## Charla técnica: Diseño de PCB y EMI

Yann Bouvier <a href="mailto:yann.bouvier@urjc.es">yann.bouvier@urjc.es</a>

José Antonio Villarejo Mañas <u>Jose.Villarejo@upct.es</u>

Miroslav Vasić <u>miroslav.vasic@upm.es</u>

David Marroquí Sempere dmarroqui@umh.es

## Introducción

## ¿Que aprenderemos/repasaremos hoy?

- Conceptos básicos y avanzados de rutado de PCB

- Consideraciones en el diseño para aumentar la densidad de potencia

- Consideraciones de puesta a tierra y de ruido de modo común y diferencial

- Revisar ejemplos prácticos y errores comunes

## ¿Por qué es importante?

- Buen diseño → Buen funcionamiento de prototipo: mayor eficiencia, menor ruido, etc.

- Reducción de costes y tiempos de rediseños

- Problemas de certificación de equipos

¡Compartir experiencias entre el público al final!

# Diseño y rutado de PCB: Nivel principiante a experimentado

Yann Bouvier <a href="mailto:yann.bouvier@urjc.es">yann.bouvier@urjc.es</a>

# ¿Magia Negra?

# Ciencia e Ingeniería

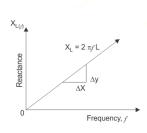

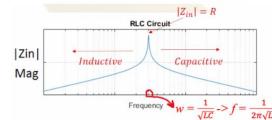

$\nabla \cdot \mathbf{D} = \rho_{V}$  $\nabla \cdot \mathbf{B} = 0$  $\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t}$

$\nabla \times \mathbf{H} = \frac{\partial \mathbf{D}}{\partial t} + \mathbf{J}$

$I = (V/Z_C)$

(r) Series Resonance

Frequency, f

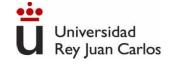

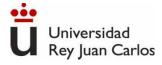

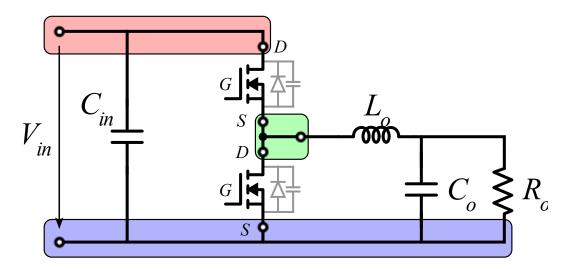

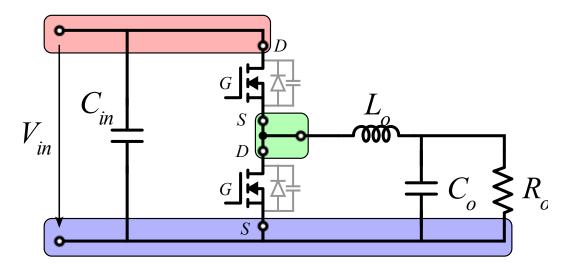

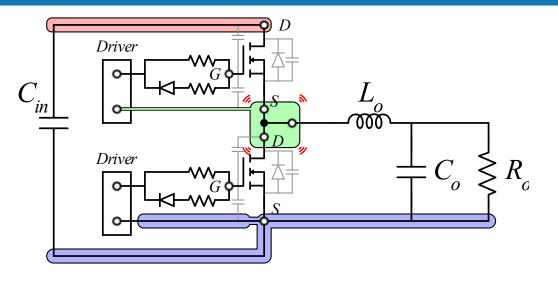

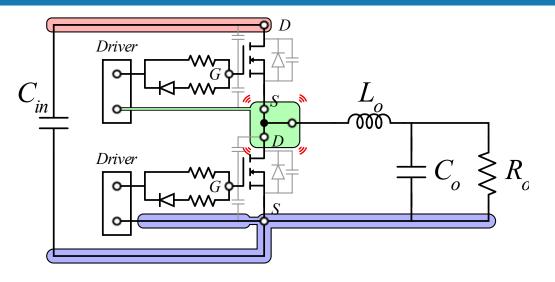

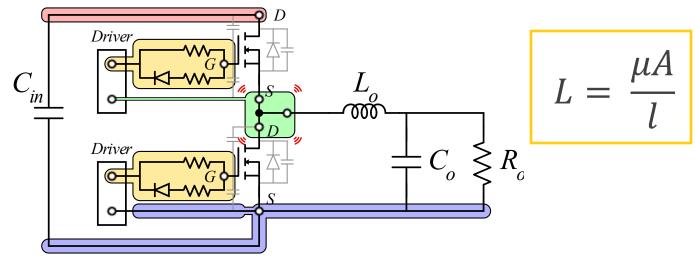

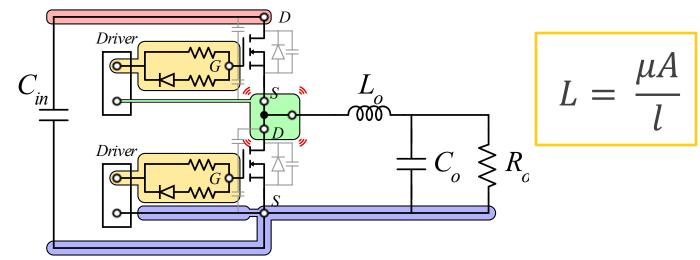

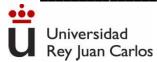

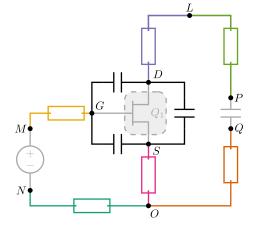

## Ejemplo de diseño de convertidor reductor

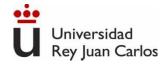

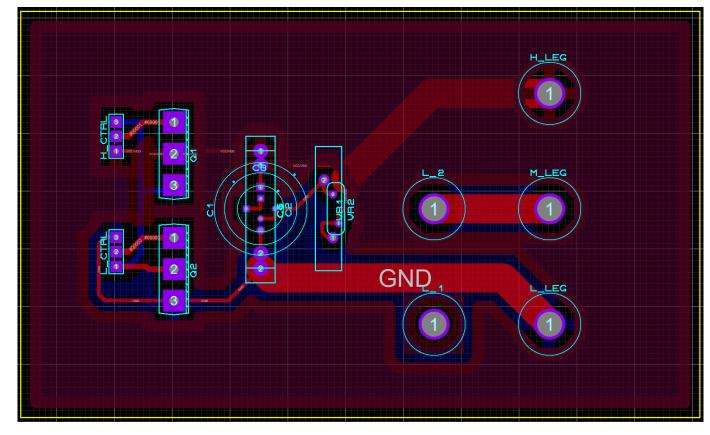

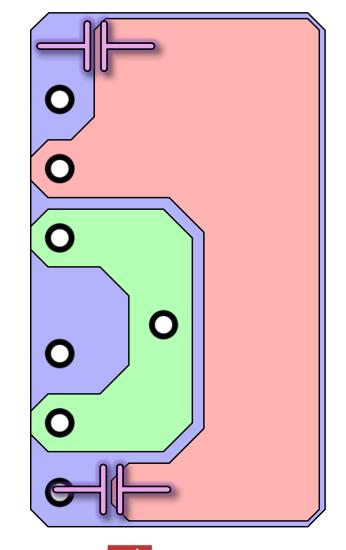

## 1ª PCB – Alumno inexperto

#### **Puntos Negativos:**

- No hay plano definido de tierra de potencia

- Muy poco condensador de bus (Cin)

- Punto ruidoso no evitado.

- El driver no esta bien definido

#### **Puntos Positivos:**

- Ángulos a 45 grados

- Condensador cerca de los transistores

## Primera aproximación de estudiante

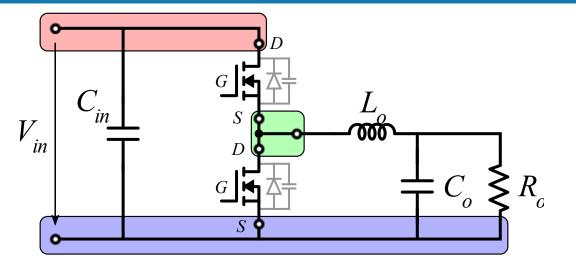

#### **Puntos Positivos:**

- Plano de tierra

- Plano de Vin solapa con la tierra

#### **Puntos Negativos:**

- Punto medio (ruidoso) solapa con la tierra

- Plano de tierra innecesariamente grande

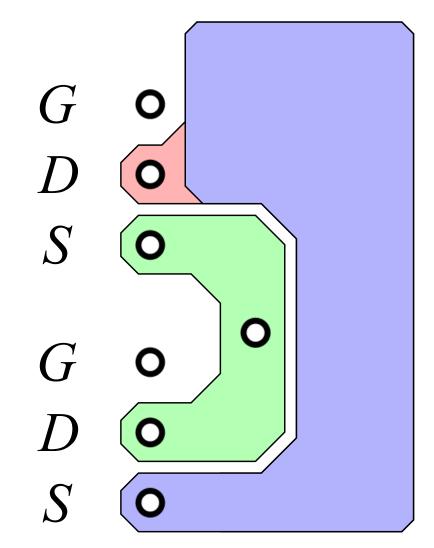

#### Objetivos para el Bus de tensión de entrada:

- Reducir la resistencia -> Menos Perdidas

- Reducir la inductancia -> Menos ruido

- Solapamiento de los dos planos -> Mas capacidad

Condensador

$$C = \frac{\varepsilon A}{d}$$

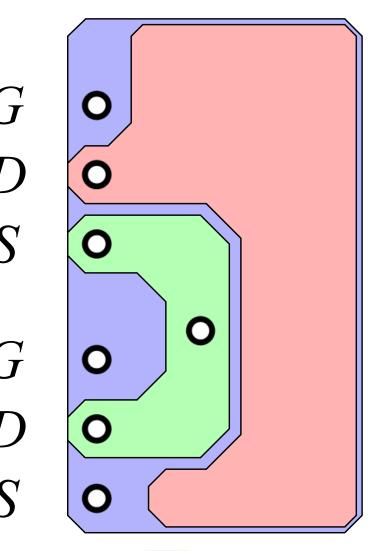

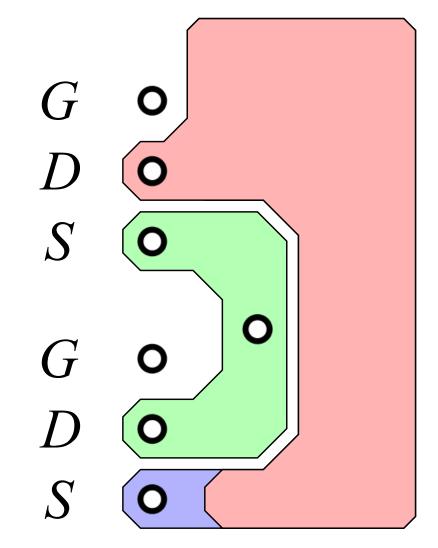

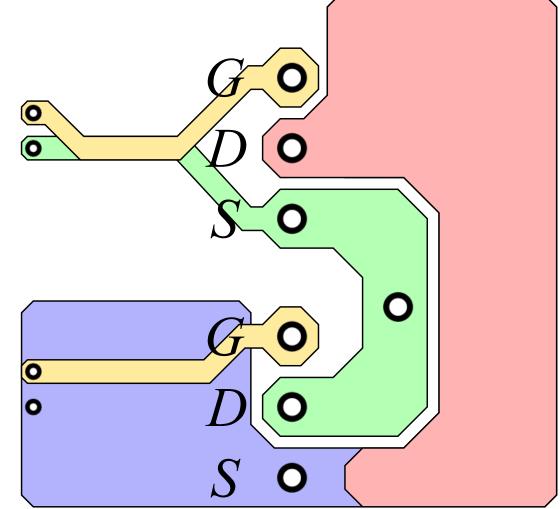

G

Bobina

$$L = \frac{\mu A}{l}$$

G

$\mathcal{L}$

S

D

S

#### Objetivos para el Bus de tensión de entrada:

- Reducir la resistencia -> Menos Perdidas

- Reducir la inductancia -> Menos ruido

- Solapamiento de los dos planos -> Mas capacidad

Condensador

$$C = \frac{\varepsilon A}{d}$$

Universidad

Rey Juan Carlos

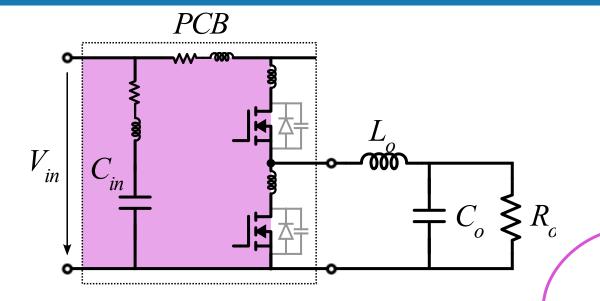

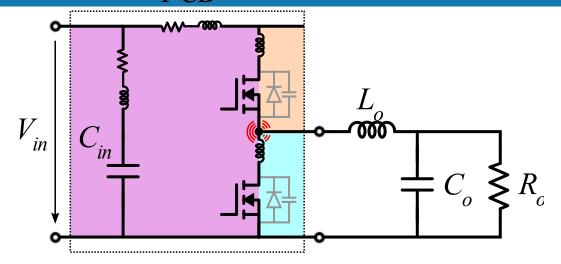

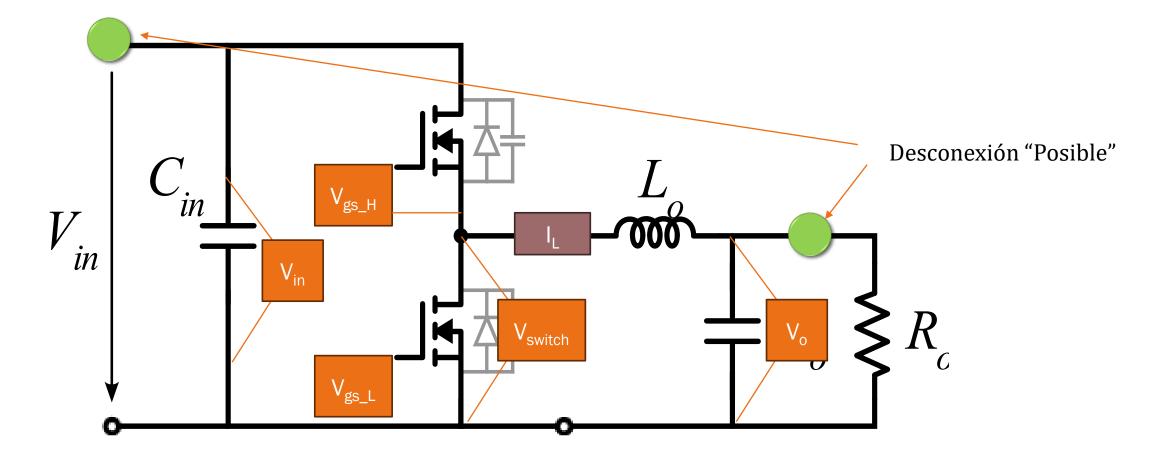

#### Punto medio ruidoso a evitar:

- Evitar solapar el punto medio con los dos otros planos

- Menos capacidad en paralelo con los transistores

- Menos energíaa perdida

- Menos radiación electromagnética

#### Capacidad parasita

$$C = \frac{\varepsilon A}{d}$$

$$\frac{dv}{dt} \uparrow \Rightarrow picos \ de \ i_c$$

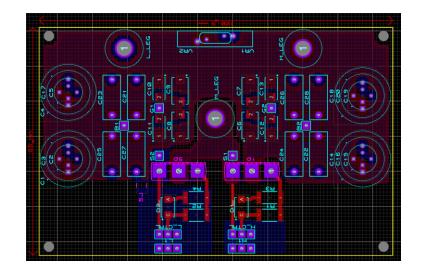

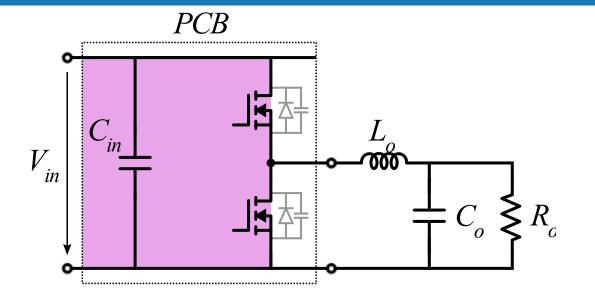

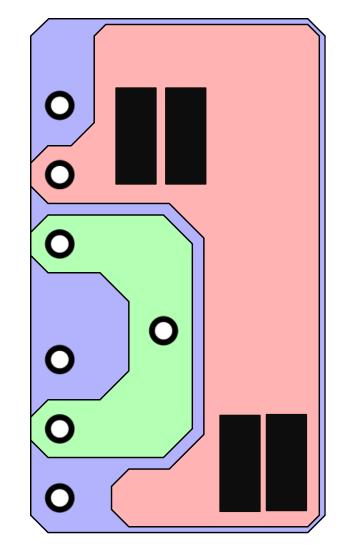

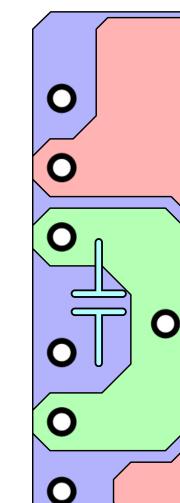

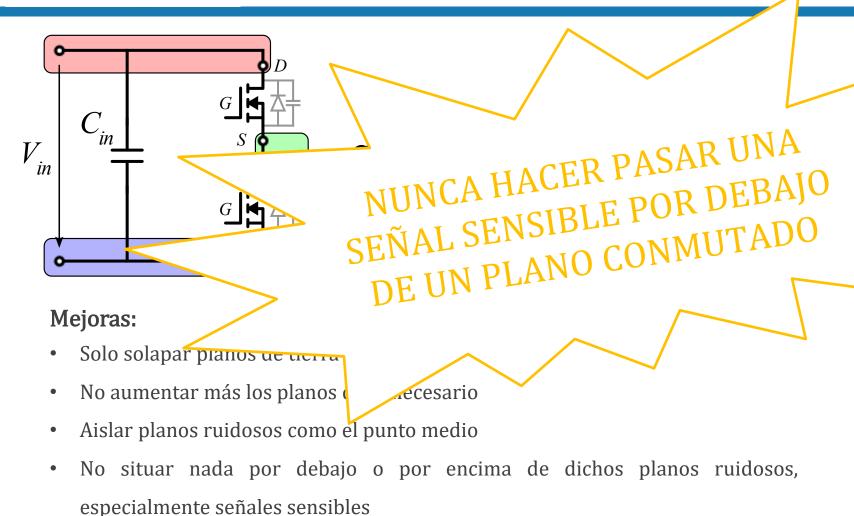

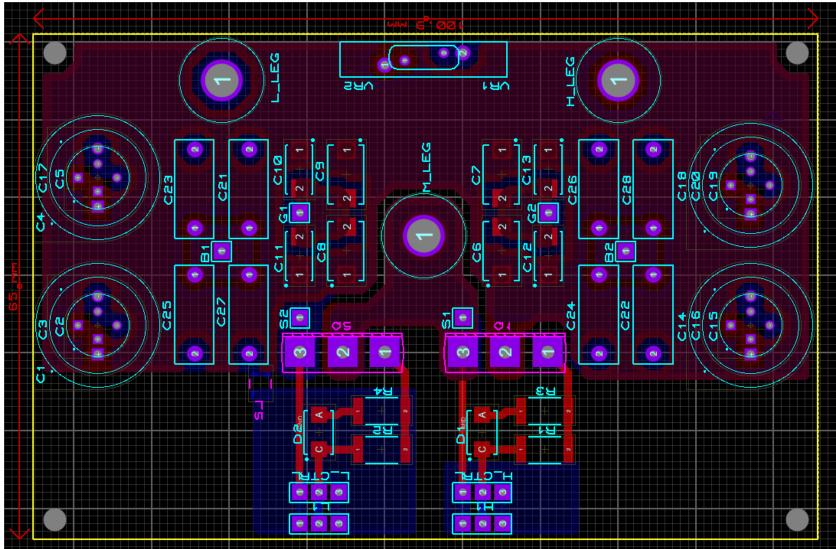

# 3ª PCB – Planos corregidos

#### Mejoras:

- Solo solapar planos de tierra y bus

- No aumentar más los planos de lo necesario

- Aislar planos ruidosos como el punto medio

- No situar nada por debajo o por encima de dichos planos ruidosos, especialmente señales sensibles

# 3ª PCB – Planos corregidos

#### Mejoras:

- Solo solapar planos de tierra y bus

- No aumentar más los planos de lo necesario

- Aislar planos ruidosos como el punto medio

- No situar nada por debajo o por encima de dichos planos ruidosos, especialmente señales sensibles

# 3ª PCB – Planos corregidos

#### Error:

• El transistor del lado alto se referencia al punto medio, pero no hay que hacer plano, como si fuera una tierra.

#### Punto positivo:

Los planos de potencia y del driver están separados y se juntan en un solo punto

#### **Error:**

• El transistor del lado alto se referencia al punto medio, pero no hay que hacer plano, como si fuera una tierra.

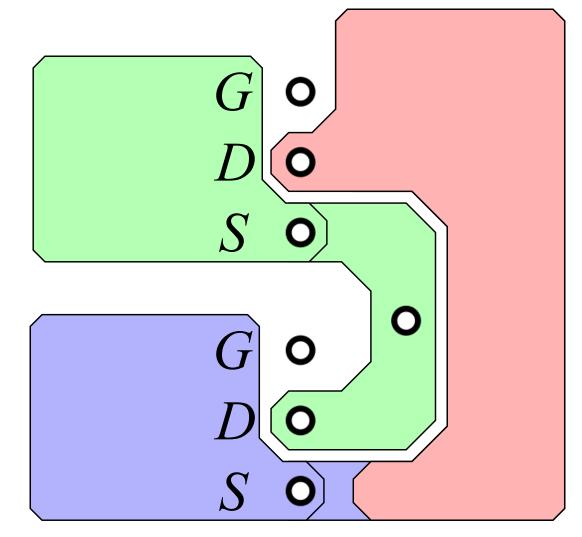

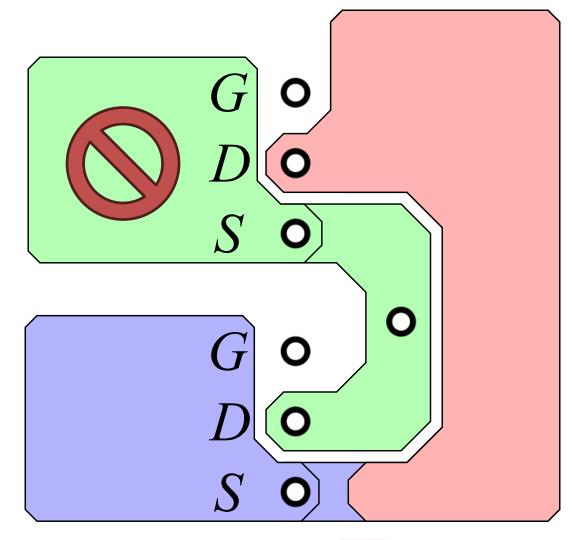

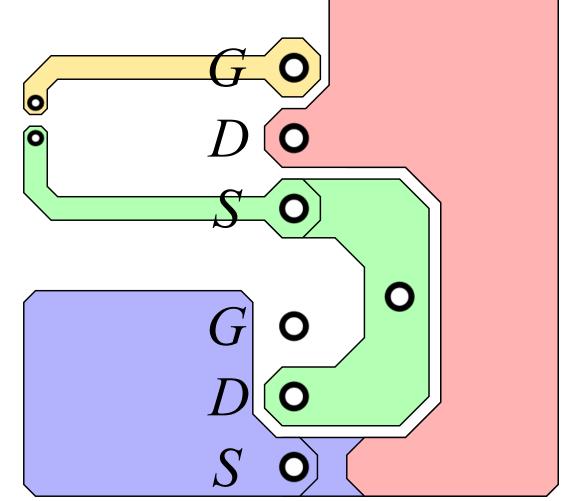

# 4ª PCB – Drivers – Mejora 1

#### Mejora:

• En la referencia del transistor del lado alto hay una pista en vez de tierra.

#### **Error:**

- El camino de ida y vuelta de la señal de encendido del transistor es corto, pero no la más corta.

- La inductancia de este camino es grande.

# 4ª PCB – Drivers – Mejora 2

#### Mejora:

• En la referencia del transistor del lado alto hay una pista en vez de tierra.

#### **Error:**

- El camino de ida y vuelta de la señal de encendido del transistor es corto, pero no la más corta.

- La inductancia de este camino es grande.

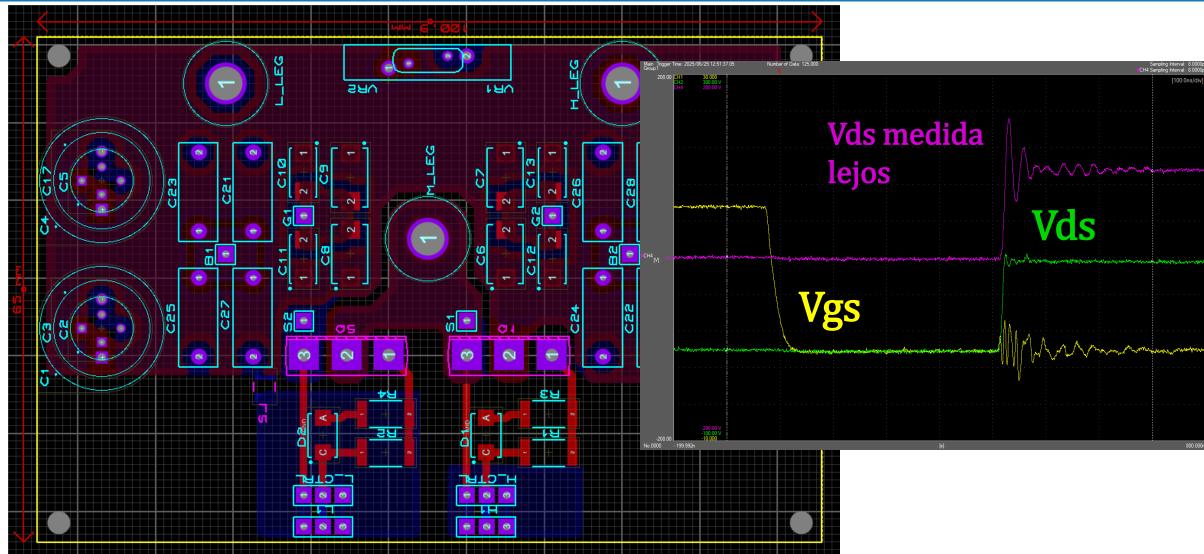

# PCB – Mejorada

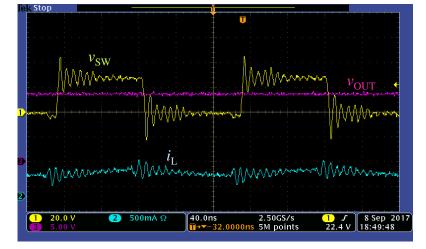

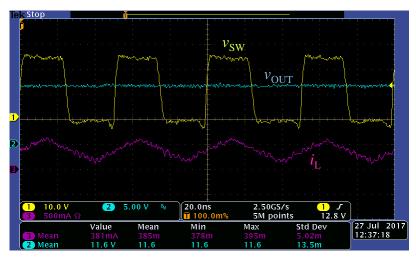

## PCB - Medidas

# PCB – Mejorada 2

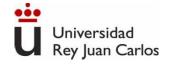

# Diseño de PCB orientado a transistores GaN y optimización de densidad de potencia

Miroslav Vasić miroslav.vasic@upm.es

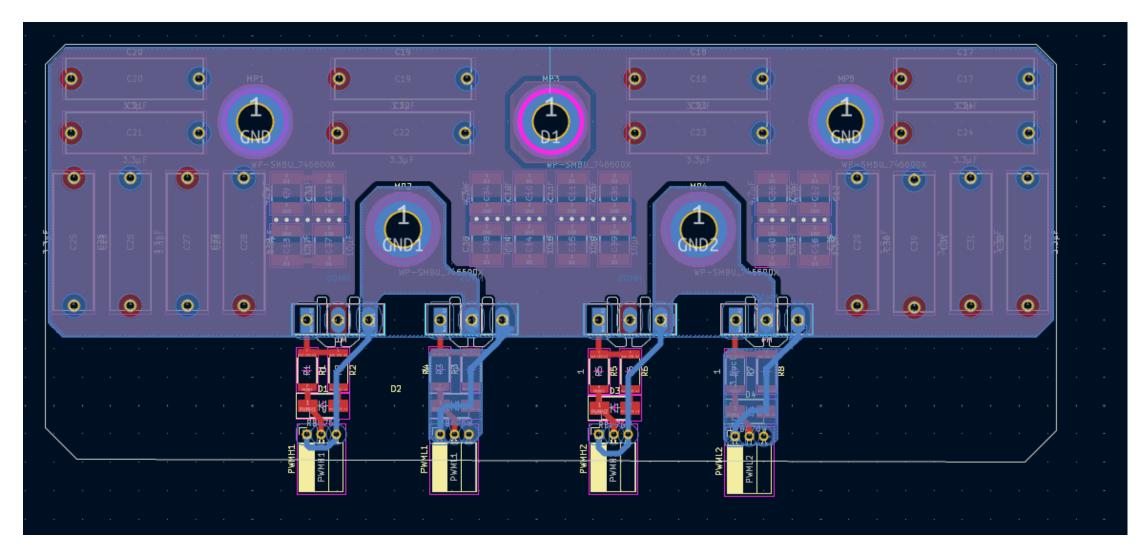

# Influencia en las perdidas de conmutación

Switching loops must be very tight!

Bad design switching at 5MHz

Efficiency: 75.1%

• Good design switching at 20MHz

Efficiency: 83%

Where is the difference??

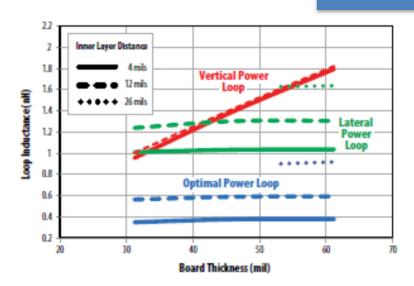

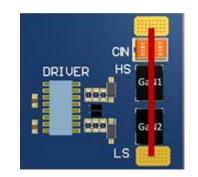

## Optimización del lazo de corriente pulsante

Lateral Power loop

U1 G 11 G 12

Vertical Power loop

Keep it as small as possible...

**Optimal Power loop**

Optimizing PCB Layout, David Reusch, Ph.D., Director, Applications, Efficient Power Conversion Corporation (www.epc-co.com)

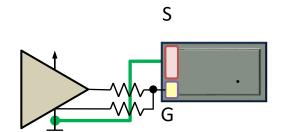

## Consideraciones para el diseño de Drivers

#### <u>Meeting Efficiency and Power Density Goals – Driving technique</u>

## Classical driving loop

The adjacent PCB layer is cut

Each via can add 1-2 nH of inductance

Flexibility in driver and on/off resistors

### 1-layer meander driving loop

Less usage of multi-layer PCBs (single layer)

No vias usage

Less inductance (faster switching)

Stiff driver and on/off resistors:

Driver with an accesible ground from 1 layer Jumping resistors (0603 on/off resistors)

vias

Classical: 3.7 nH

1-layer meander: 2.7 nH

**HFSS** simulation

## Caso real 1

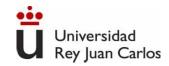

## "Termination Effect"

Secondary termination (SR + capacitor) is crucial

May lead to high leakage inductance → high AC resistance (power losses)

In general, try to overlap the primary and the secondary turns as much as posible

Lateral, vertical and on-winding termination

## "Termination Effect"

## Caso real 2

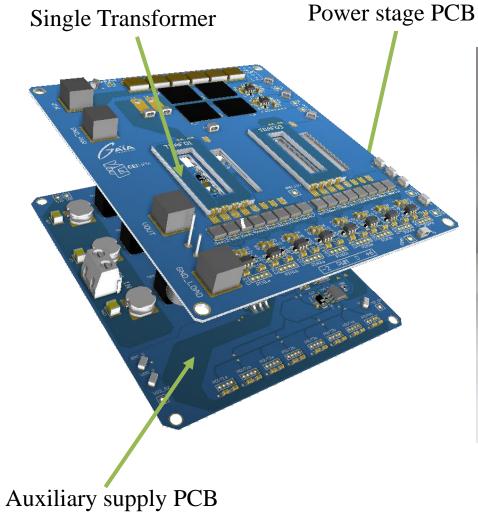

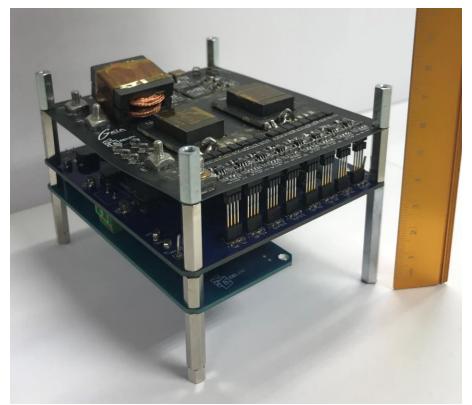

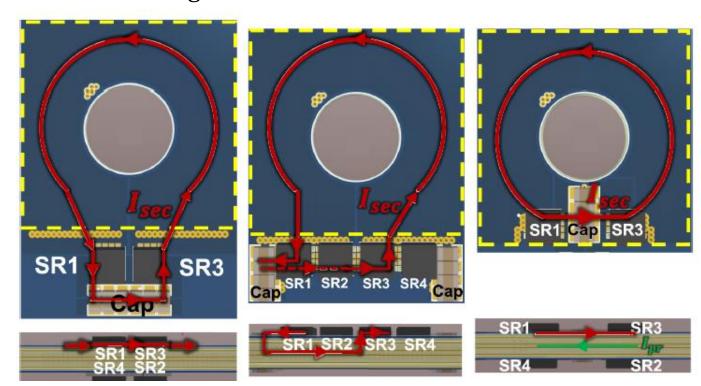

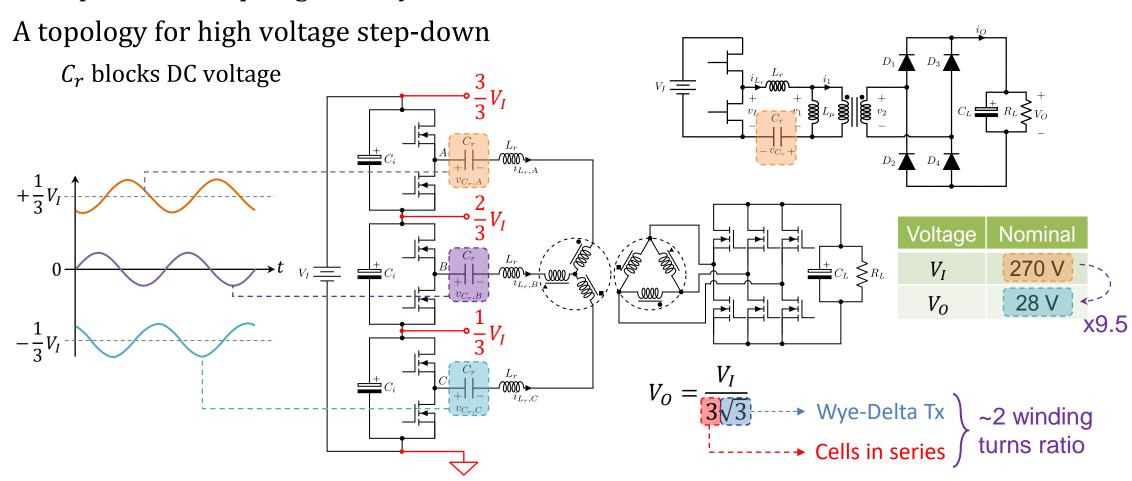

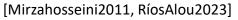

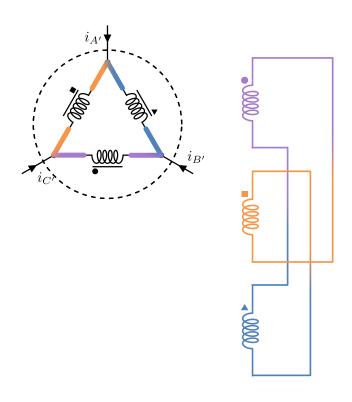

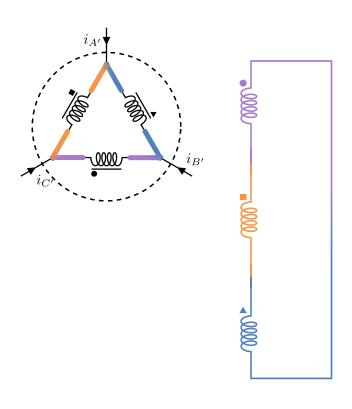

#### <u>Multiphase LLC topologies – Wye-Delta Three-Phase LLC in Stack</u>

## Consideraciones de Diseño

#### <u>Meeting Efficiency and Power Density Goals – Delta connection</u>

The Star Connection is straightforward (neutral connected on the bottom)

The Polygon Connection is more complicated

[Ríos2024]

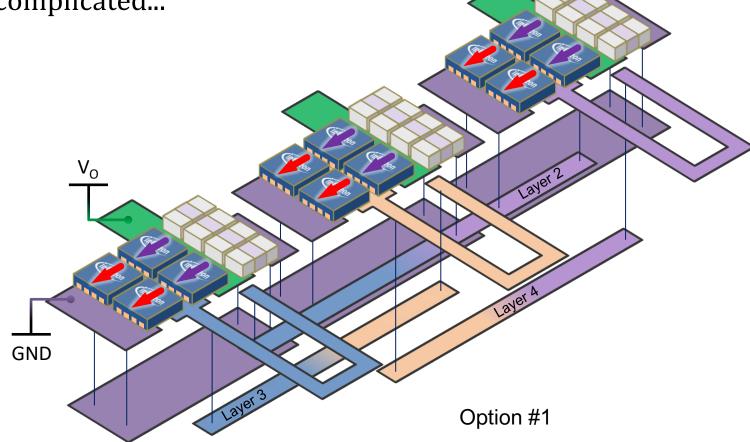

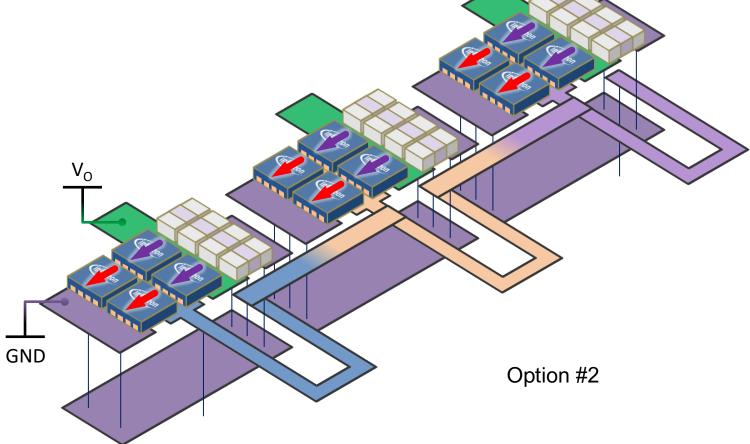

## Consideraciones de Diseño

<u>Meeting Efficiency and Power Density Goals – Delta connection</u>

The Delta Connection is more complicated...

## Consideraciones de Diseño

## <u>Meeting Efficiency and Power Density Goals – Delta connection</u>

The Delta Connection is more complicated...

## Referencias

[deJuan2022] A. de Juan, D. Serrano, P. Alou, J. -N. Mamousse, R. Deniéport and M. Vasic, "High-Frequency LLC Converter with Narrow Frequency Variations for Aircraft Applications," 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 2022, pp. 2098-2105, doi: 10.1109/APEC43599.2022.9773409.

[Prakesh2024] P. R. Prakash *et al.*, "A 2400 W/in3 1.8 V Bus Converter Enabling Vertical Power Delivery for Next-Generation Processors," *2024 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Long Beach, CA, USA, 2024, pp. 910-917, doi: 10.1109/APEC48139.2024.10509453

[Mirzahosseini2011] R. Mirzahosseini and F. Tahami, "A phase-shift three-phase bidirectional series resonant DC/DC converter," IECON 2011 - 37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 2011, pp. 1137-1143, doi: 10.1109/IECON.2011.6119468.

[RíosAstudillo2024] D. R. Linares, M. Astudillo and M. Vasić, "Optimal Driving Strategies for GaN HEMT: A Numerical Non-Linear Datasheet-Based Model," 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2024

[RíosAlou2023] D. R. Linares, M. Vasić and P. A. Cervera, "Three-Phase LLC DC/DC Converter in Stack Configuration: A Topology for High-Voltage Conversion Ratio Applications," 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 2023, pp. 1747-1752, doi: 10.1109/APEC43580.2023.10131367.

[Ríos2024] D. R. Linares, A. D. Expósito and M. Vasić, "High-Gain High-Frequency Three-Phase LLC Resonant Converter Design Based on the Wye–Delta Transformer for Aircraft Applications," in IEEE Transactions on Power Electronics, vol. 39, no. 4, pp. 4367-4383, April 2024, doi: 10.1109/TPEL.2023.3339973.

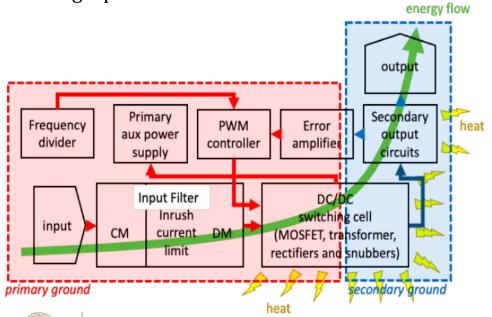

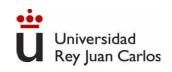

# Reducción de Interferencias Electromagnéticas en Convertidores de Potencia para Aplicaciones Espaciales

Experiencias obtenidas del proyecto Reduction of Electromagnetic Interference from Power Converters and Filters 4000134628/21/NL/F (ESA)

J.A. Carrasco, F. García de Quirós

A. Garrigós, J.M.Blanes, **D.Marroquí**

E. Sanchis-Kilders, J.B. Ejea

I. de la Viuda, M. Cora

# Contexto y objetivos

#### **Contexto**

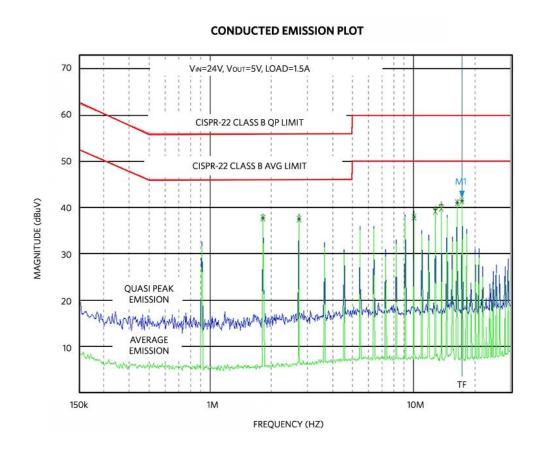

- <u>La reducción de EMI es crítica</u> en aplicaciones espaciales debido a la alta densidad de equipos electrónicos sensibles.

- Los convertidores <u>DC-DC son fuentes significativas</u> de EMI conducida y radiada.

- Este estudio investiga diversas técnicas de diseño y configuración para minimizar la EMI en convertidores DC-DC de potencia media.

#### **Objetivos Principales:**

Mediante el uso de tarjetas "fácilmente <u>reconfigurables</u>" evaluar comparativamente:

- 1. El impacto de diferentes topologías de filtro.

- Límites inferiores al estándar: ECSS-E-ST-20-07C

- DM: >20 dB por debajo del límite.

- CM: >25 dB por debajo del límite.

- 2. Analizar la influencia de distintas configuraciones de *grounding*.

- 3. Proponer recomendaciones de diseño basadas en resultados experimentales.

# Especificaciones

**Especificaciones principales** – La justificación queda fuera de esta presentación.

Tensión de entrada nominal: 28 V (25 V – 30 V)

Tensión de salida nominal: 5 V - Potencia de salida media: 30 W - Potencia pico: 36 W

• Frecuencia de conmutación: 125 kHz

Tensiones de salida auxiliares: +12V y -12V

Potencia de salida media: 500mW

• Topología push-pull

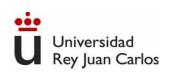

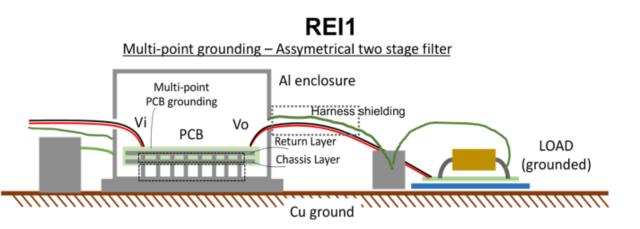

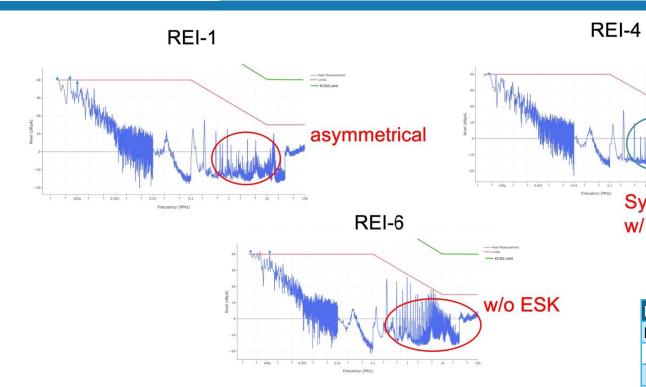

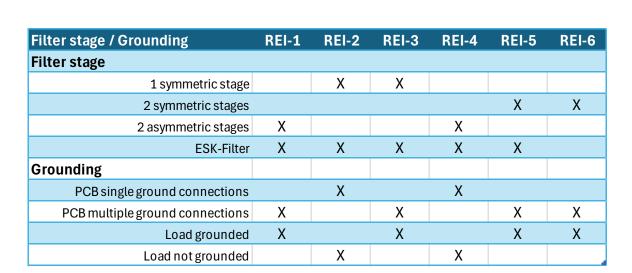

#### Se evaluaron 6 diseños con configuraciones diferentes

| Filter stage / Grounding        | REI-1 | REI-2 | REI-3 | REI-4 | REI-5 | REI-6 |

|---------------------------------|-------|-------|-------|-------|-------|-------|

| Filter stage                    |       |       |       |       |       |       |

| 1 symmetric stage               |       | Χ     | Χ     |       |       |       |

| 2 symmetric stages              |       |       |       |       | Χ     | Χ     |

| 2 asymmetric stages             | Χ     |       |       | Χ     |       |       |

| ESK-Filter                      | Χ     | Χ     | Χ     | Χ     | Χ     |       |

| Grounding                       |       |       |       |       |       |       |

| PCB single ground connections   |       | Χ     |       | Χ     |       |       |

| PCB multiple ground connections | Χ     |       | Χ     |       | Χ     | Χ     |

| Load grounded                   | Χ     |       | Χ     |       | Χ     | Χ     |

| Load not grounded               |       | Χ     |       | Χ     |       |       |

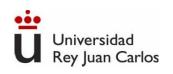

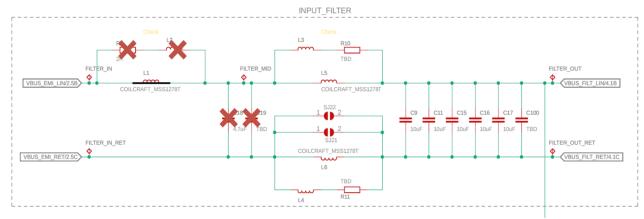

# Topologías de filtros

#### Filtro de entrada común "reconfigurable":

#### Filtro Asimétrico (REI-1, REI-4):

- Línea positiva.

- Potencial desbalance de impedancia.

#### Filtro Simétrico (REI-2, REI-3, REI-5, REI-6):

- Distribuidos en línea positiva y de retorno.

- Busca un mejor balance de impedancia.

#### Configuración simétrica

Configuración asimétrica

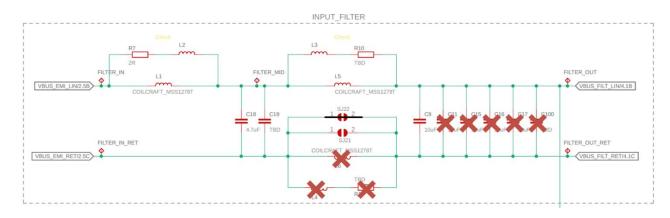

# Filtro de modo común y concepto ESK

#### **Concepto de Filtro ESK:**

- Introducción de un filtro DM y CM adicional <u>muy cercano</u> a la celda de conmutación.

- Objetivo: Contener el ruido de alta frecuencia lo más cerca posible de su fuente.

# Estrategias de puesta a tierra

# Estrategias de puesta a tierra

La configuración de la puesta es común, pero "reconfigurable" para poder realizar comparativas. Se investigaron:

#### Puesta a Tierra Monopunto:

- La configuración "más tradicional"

- Puede presentar alta impedancia a altas frecuencias.

#### **Puesta a Tierra Multipunto:**

- Recomendada para altas frecuencias, ofrece un camino de baja impedancia para corrientes de CM.

- Conexión del plano de masa secundario al chasis en múltiples puntos.

#### Puesta a Tierra de la Carga:

- Carga aislada vs. carga referenciada al chasis.

- Impacta significativamente en las corrientes de modo común.

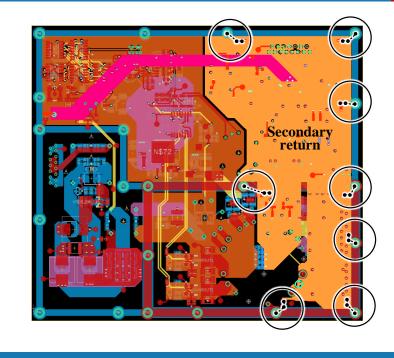

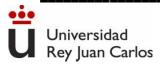

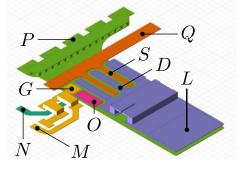

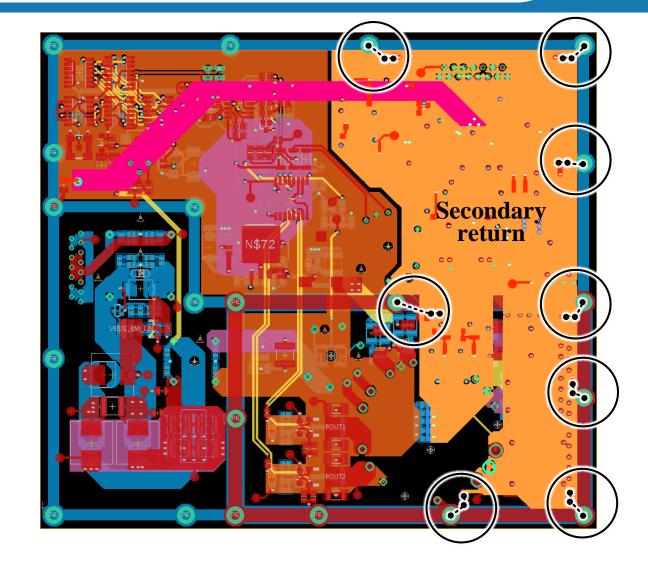

# Diseño de Tarjeta

# Diseño de PCB

#### Consideraciones a la hora de realizar el diseño:

- Se busca minimizar la inductancia y capacitancia parásitas de pistas, capas, planos de tierra, áreas de cobre y vías.

Especialmente en la celda de conmutación.

- 2. Colocación basada en el **flujo de energía natural** de la placa.

- 3. Consideración de las restricciones de **disipación de calor** y la ubicación de **fuentes de ruido** o circuitos sensibles al ruido para reordenar los grupos.

# Diseño de PCB

#### Consideraciones a la hora de realizar el diseño:

#### 1. Puesta a Tierra Multipunto reconfigurable

- 2. Stack-up elementos clave

- Capa Superior:

- Pistas +5Vs para el condensador de la celda de conmutación.

- Plano de chasis.

- Capa Interna 1:

- Señales MOSFET (con sus retornos).

- Líneas de +15Vs, -15Vs, y +5Vs.

- Capa Interna 2:

- Plano de chasis para disipación de calor.

- Capa Interna 3:

- Tensiones secundarias de CC: +15Vp, +15Vs, -15Vs, +5Vs.

- Capa Interna 4:

- Retornos secundarios de CC: +15Vs\_ret, -15Vs\_ret, +5Vs\_ret.

- Capa Inferior:

- Plano de chasis.

- Pistas +15Vp\_ret.

# Resultados y conclusiones

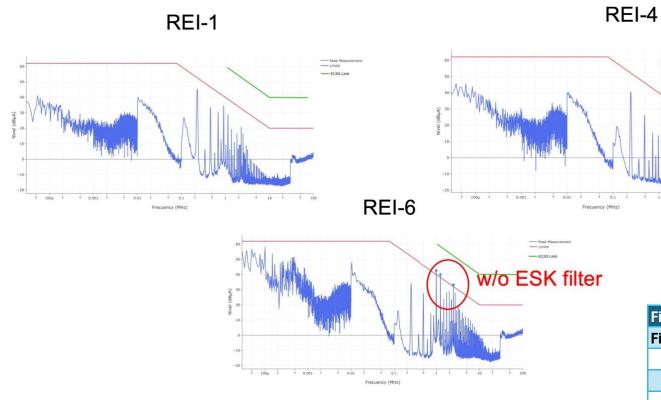

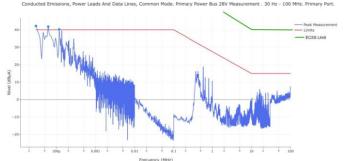

# DM emisiones en la alimentación

Single-ground

#### **Destacable:**

Los buenos resultados de REI-1 y REI-4, con filtrado asimétrico y

doble etapa de filtrado son las más prometedoras, llegando a

compensar las carencias de la conexión a tierra simple (REI-4)

| Filter stage / Grounding        | REI-1 | REI-2 | REI-3 | REI-4 | REI-5 | REI-6 |

|---------------------------------|-------|-------|-------|-------|-------|-------|

| Filter stage                    |       |       |       |       |       |       |

| 1 symmetric stage               |       | Χ     | Χ     |       |       |       |

| 2 symmetric stages              |       |       |       |       | Χ     | Χ     |

| 2 asymmetric stages             | Χ     |       |       | Χ     |       |       |

| ESK-Filter                      | Χ     | Χ     | Χ     | Χ     | Χ     |       |

| Grounding                       |       |       |       |       |       |       |

| PCB single ground connections   |       | Χ     |       | Χ     |       |       |

| PCB multiple ground connections | Χ     |       | Χ     |       | Х     | Χ     |

| Load grounded                   | Χ     |       | Χ     |       | Χ     | Χ     |

| Load not grounded               |       | Χ     |       | Χ     |       |       |

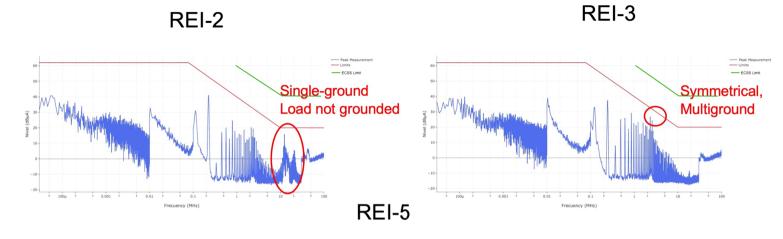

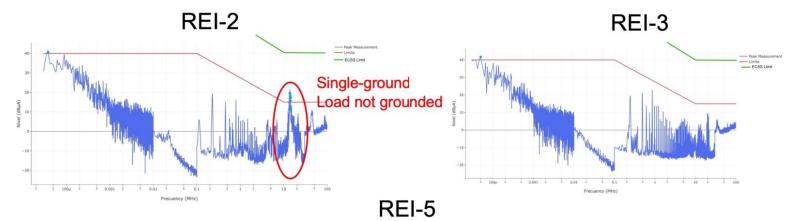

## DM emisiones en la alimentación – filtro simétrico

Mismatch de Bobinas importante!

#### **Destacable:**

• REI-2, REI-3 y REI-5 de filtrado simétrico. cualquier desequilibrio aumentará el **ruido con armónicos a frecuencias intermedias y altas**.

| Filter stage / Grounding        | REI-1 | REI-2 | REI-3 | REI-4 | REI-5 | REI-6 |

|---------------------------------|-------|-------|-------|-------|-------|-------|

| Filter stage                    |       |       |       |       |       |       |

| 1 symmetric stage               |       | Χ     | Χ     |       |       |       |

| 2 symmetric stages              |       |       |       |       | Χ     | Χ     |

| 2 asymmetric stages             | Χ     |       |       | Χ     |       |       |

| ESK-Filter                      | Χ     | Χ     | Χ     | Χ     | Χ     |       |

| Grounding                       |       |       |       |       |       |       |

| PCB single ground connections   |       | Χ     |       | Χ     |       |       |

| PCB multiple ground connections | Χ     |       | Χ     |       | Χ     | Χ     |

| Load grounded                   | Χ     |       | Χ     |       | Χ     | Χ     |

| Load not grounded               |       | Χ     |       | Χ     |       |       |

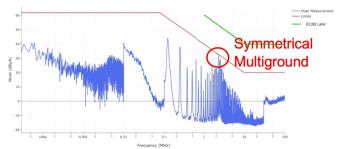

# CM emisiones en la alimentación

Symmetrical

w/ ESK

## CM emisiones en la alimentación – filtro simétrico

| Filter stage / Grounding        | REI-1 | REI-2 | REI-3 | REI-4 | REI-5 | REI-6 |

|---------------------------------|-------|-------|-------|-------|-------|-------|

| Filter stage                    |       |       |       |       |       |       |

| 1 symmetric stage               |       | Χ     | Χ     |       |       |       |

| 2 symmetric stages              |       |       |       |       | Χ     | Χ     |

| 2 asymmetric stages             | Χ     |       |       | Χ     |       |       |

| ESK-Filter                      | Χ     | Χ     | Χ     | Χ     | Χ     |       |

| Grounding                       |       |       |       |       |       |       |

| PCB single ground connections   |       | Χ     |       | Χ     |       |       |

| PCB multiple ground connections | Χ     |       | Χ     |       | Χ     | Χ     |

| Load grounded                   | Χ     |       | Χ     |       | Χ     | Χ     |

| Load not grounded               |       | Χ     |       | Χ     |       |       |

# Conclusiones y sugerencias de diseño:

- 1. Optar por filtrado asimétrico de doble etapa o simétrico muy bien equilibrado

- Si se elige un filtrado simétrico, este debe estar "muy bien equilibrado" (como el de REI-5) para obtener un rendimiento óptimo y evitar un aumento del ruido en frecuencias intermedias y altas

- 2. La conexión a **tierra multipunto es la mejor opción**, especialmente para la atenuación del modo común (CM). REI-4 (punto único) es la excepción que confirma la norma.

- 3. La inclusión de un **filtro ESK** (DM y CM adicional <u>muy cercano</u> a la fuente de ruido) ha demostrado una **mejora** general en la reducción de EMI.

- 4. Es fundamental llevar a cabo una **buena caracterización de los componentes** utilizados para el filtrado (especialmente si son COTs). La inclusión de parásitos no previstos o desbalanceos pueden repercutir negativamente en la reducción de EMI.

- **5. El diseño del PCB es crítico**. Reducción de parásitos, evitar ranurar planos de masa y uso de cables trenzados para el cableado de alimentación también ayuda a equilibrar las impedancias de la línea.

# Hacer que funcione el prototipo

José Antonio Villarejo Mañas

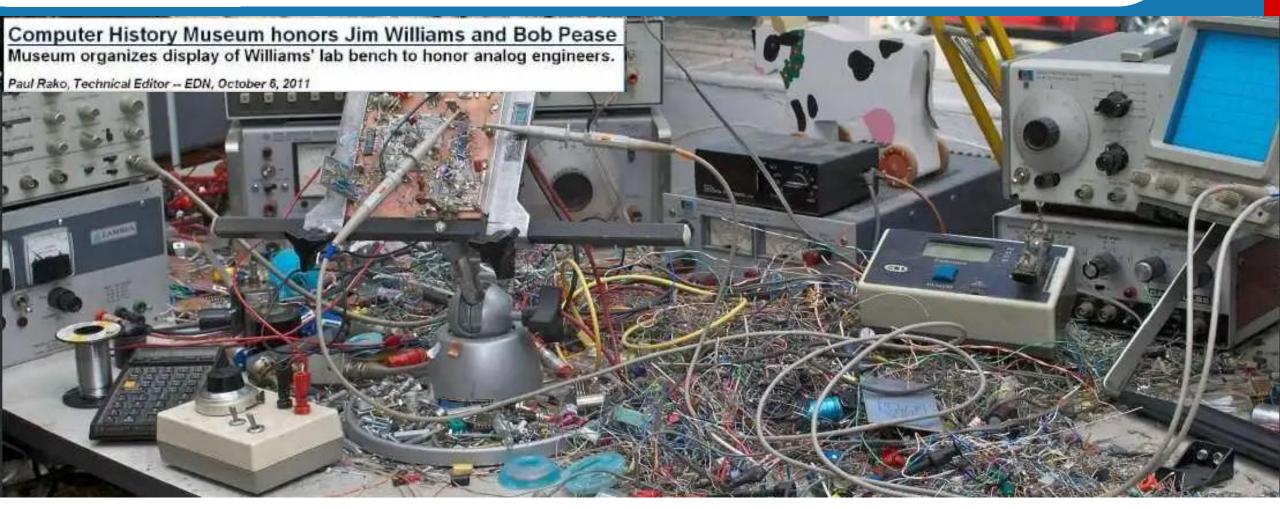

# Bob Pease and Jim Williams. SERIES FOR DESIGN ENGINEERS ROBERT A. PEASE **Analog** Troubleshooting **Circuit** Analog Circuits Design National EDN SERIES FOR DESIGN ENGINEERS Art, Science, and Personalities Edited by Jim Williams

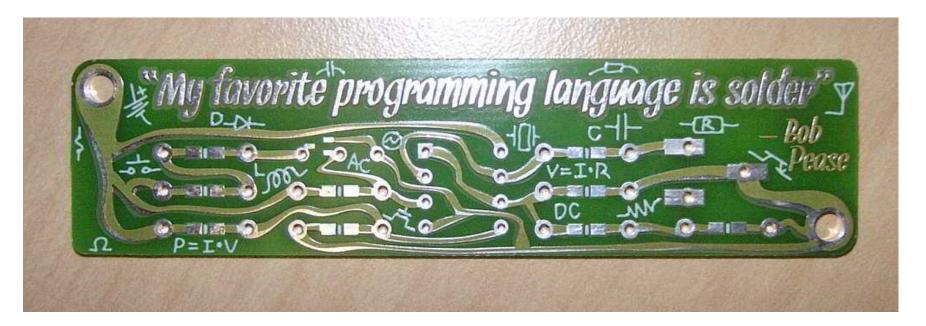

## Remembering Bob Pease.

### Sin duda una de mis citas favoritas

# ¿Qué significa "hacer que funcione"?

#### Has decidido construir un prototipo de potencia

# ¿Tienes preparadas...?

- Hojas de cálculo

- Simulaciones

- Selección de componentes reales

- Simulaciones con los nuevos componentes

- Cálculo aproximado de pérdidas

# ¿Qué significa "hacer que funcione"?

cia

Has deci S

Si no es así, yo me lo pensaría

# ¿Tienes preparadas...?

- Hojas de cálculo

- Simulaciones

- Selección de componentes reales

- Simulaciones con los nuevos componentes

- Cálculo aproximado de pérdidas

# Errores que puedes detectar en esta etapa

- 1. Errores "tontos" de cálculo o de concepto.

- 2. Selección inapropiada de anchos de banda en operacionales

- 3. Selección inapropiada del tipo de operacionales

- 4. Tiempos muertos insuficientes, **circuitos de disparo inapropiados**...

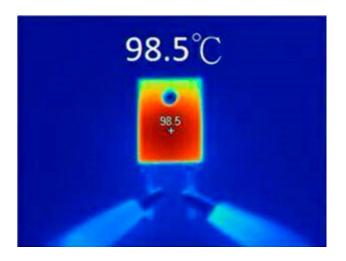

- 5. Necesidad de disipadores

- ☐ Construyo el prototipo con las recomendaciones del SAAEI

- ☐ Lo conecto y funciona

# ¡Esto está terminado en dos días!

- ☐ Construyo el prototipo con las recomendaciones del SAAEI

- ☐ Lo conecto y funciona

# ¡Esto está terminado en dos días!

# No solo debes pensar en **que debe hacer** tu circuito

# También hay que pensar como lo vas a probar

- Dejar puentes para separar partes del circuito

- Separar desde el principio masas de potencia y señal

- Puntos de prueba, también para la corriente

Planifica las pruebas desde el diseño

# ¿Qué aporta la planificación? Ejemplo

# Vout with clip-on method Clip-on method T# - X To file venie rentate to the tipe circus means that the tecture Avera times he ster Clymand sty Vour ripple = ~20mV

# ¿Qué aporta la planificación? Ejemplo

# Pigtail method Vour with pigtail method Vertal Nwed by Vour ripple = ~9mV

# ¿Qué aporta la planificación? Ejemplo

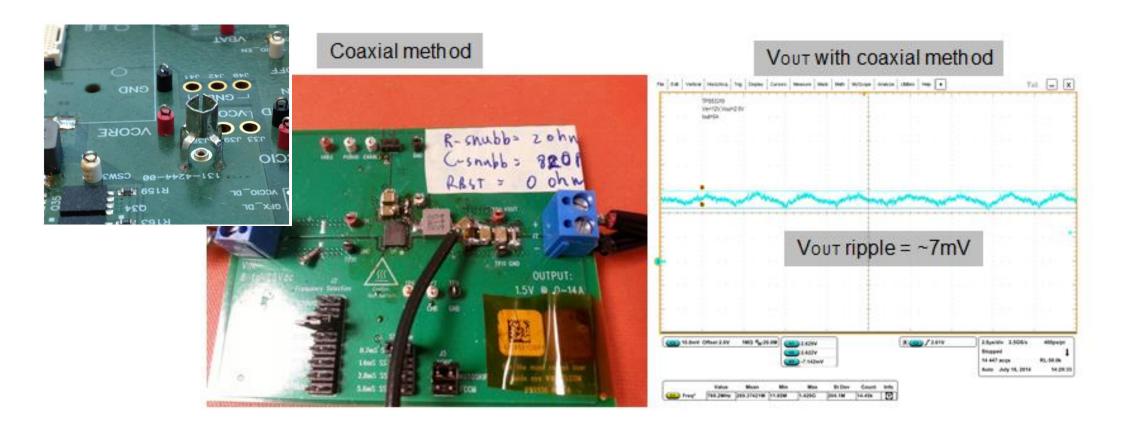

La mejor opción soldar un cable coaxial o dejar preparado un conector "similar" https://www.ti.com/document-viewer/lit/html/SSZTB25

# Puntos de prueba desde el inicio del diseño

1. Caracterizar los **componentes pasivos**

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- Tiempos puertos

- dV/dt en la puerta

- Consumo ≈ "drivers"

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- 3. Pruebas a baja tensión

- Funcionamiento global

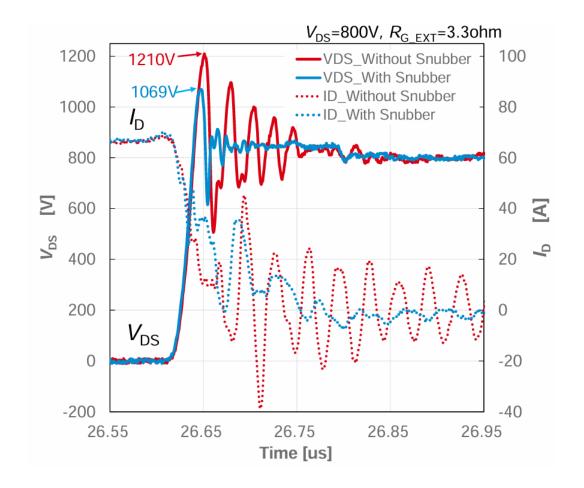

- Determinar si son necesarios los Snubbers

- Saturación de magnéticos

- Pérdidas en conducción

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- 3. Pruebas a baja tensión

- 4. Snubbers//conmutaciones

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- 3. Pruebas a baja tensión

- 4. Snubbers//conmutaciones

- 5. Protecciones

Aunque las protecciones es interesante tenerlas funcionando cuanto antes para proteger nuestro circuito, en ocasiones no responden bien, hasta que no están limpias las conmutaciones. Los ruidos pueden disparar las protecciones.

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- 3. Pruebas a baja tensión

- 4. Snubbers//conmutaciones

- 5. Protecciones

- 6. Pruebas a incrementando la carga

- Formas de onda seguras

- · Rizado a la salida

- Corriente y tensión en L

- Rendimiento

- Temperaturas

- Comparativa con valores esperados

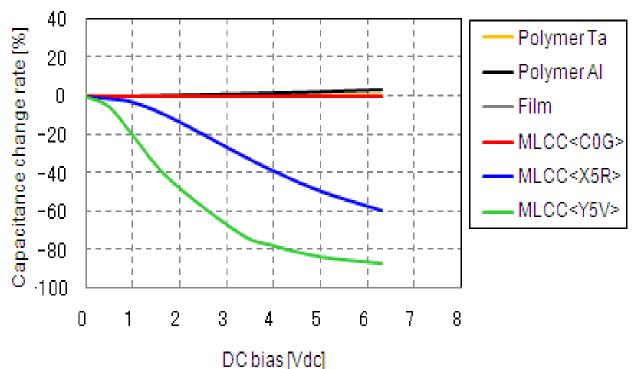

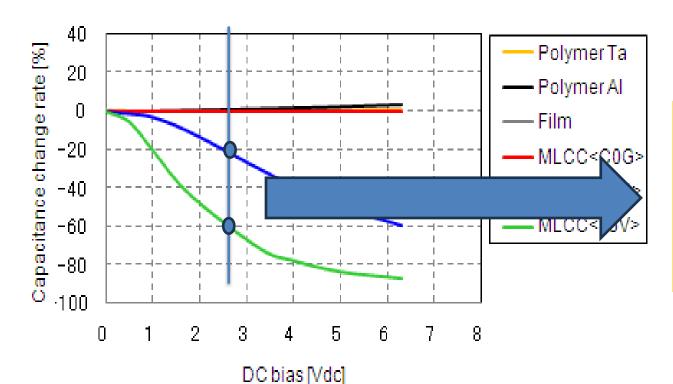

# **Posibles causas:**

- Incremento del ESR

- Capacidad menor de la esperada

## **Posibles causas:**

- Incremento del ESR

- Capacidad menor de la esperada

## **Posibles causas:**

- Incremento del ESR

- Capacidad menor de la esperada

Pérdidas de capacidad entre el 20 y el 70% dependiendo el dieléctrico del condensador

## Pruebas recomendadas

- 1. Caracterizar los componentes pasivos

- 2. Alimentación auxiliar y disparos

- 3. Pruebas a baja tensión

- 4. Snubbers//conmutaciones

- 5. Protecciones

- 6. Pruebas a incrementando la carga

- 7. Cerrar el lazo

## Pruebas recomendadas: Cerrar el lazo

- 1. Utiliza cargas electrónicas y fuentes limitadas

- 2. Te puedes equivocar con facilidad en las resistencias y condensadores del lazo

- 3. Carga **resistiva** inicialmente y potencia **moderada**.

- 4. Empieza de forma conservadora **f0dB muy baja**

- 5. Puede ser el momento de obtener la respuesta real de la potencia (Bode)

- 6. Mejora el diseño **aumente f0dB**

- 7. Mediante transitorios generados por la carga electrónica puedes comprobar que la simulación y el prototipo se comportan de forma similar

# Errores Comunes en esta etapa

- 1. No limitar las fuentes, o poner demasiada carga

- 2. No analizar el arranque

- 3. No limitar la acción integral

- 4. No **acotar** las **señales de control** válidas

- 5. No **probar todas las condiciones** de tensión y carga

- 6. Las simulaciones ayudan, pero lo que simulas se tiene que parecer a la realidad. **Modifica la simulación** para que se parezca a la realidad.

# Tu circuito ha funcionado durante un tiempo

# Hasta que....

Si las temperaturas no eran altas, porque lo has comprobado Si las señales no eran ruidosas, porque lo has comprobado Si el lazo funcionaba bien, porque lo has ......

#### ¿Qué puede haber pasado?

Hay problemas que no se detectan hasta pasados meses de funcionamiento Hay problemas que no se detectan hasta pasados años de funcionamiento Hay problemas que no se detectan porque no se comprobaron

# Causas típicas

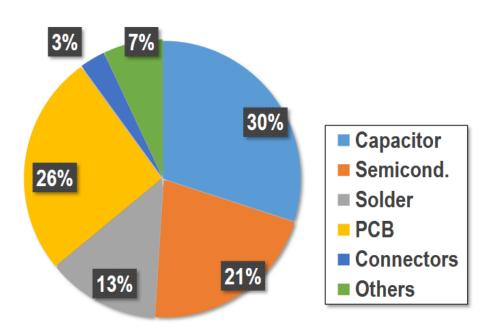

#### Breakdown of Failure in Power Electronics (2007) [2]

[1]. Y. Avenas et al., IEEE Ind. Electron. Mag., vol. 9, No. 4, pp. 22-36, Dec. 2015.

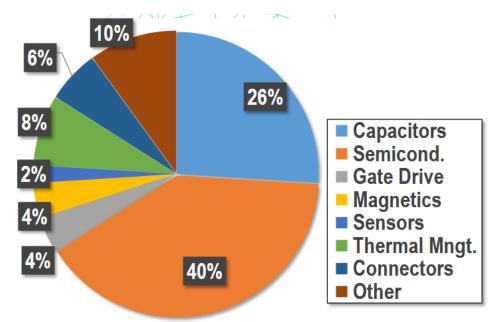

# Components in need of reliability improvements (2018) [3]

- [2]. S. Yang et al., IEEE Trans. Power Electron., vol. 25, no. 11, pp. 2734-2752, Nov. 2010.

- [3]. J. Falck et al., IEEE Ind. Electron. Mag., pp. 24-35, 2018.

https://www.psma.com/sites/default/files/Failure%20Modes%20and%20Conditional%20Monitoring%20Techniques%20for%20Capacitors%20%28Mark%20Scott%2C%20Miam i%20University%29.pdf?utm\_source=chatgpt.com

# Condensadores – Buenos candidatos para fallos

| Tecnología                            | Cortocircuito    | Circuito abierto<br>/↑ESR | Valor "drifteado" | Nota                                       |

|---------------------------------------|------------------|---------------------------|-------------------|--------------------------------------------|

| Electrolítico(Aluminio)               | ✓                | ✓                         | ✓                 | Válvula de seguridad, secado               |

| Electrolítico(Polímero)               | _                | ✓                         | ✓                 | Más estable que electrolítico convencional |

| Tántalo (MnO <sub>2</sub> / polímero) | <b>√</b> (≈57 %) | <b>√</b> (~32 %)          | <b>√</b> (~11 %)  | Riesgo térmico y fuego                     |

| Cerámico MLCC                         | <b>√</b> (~49 %) | <b>√</b> (~22 %)          | <b>√</b> (~29 %)  | Fisuras por estrés                         |

| Film (PP/MPPF)                        | ~                | ✓                         | ✓                 | Auto-curación, adecuado para AC            |

Pero pueden pasar "mil" cosas, te voy a contar algunas historias.....

# Working Voltage vs Isolation Voltage

#### Parámetros de un optoacoplador:

| Parámetro                                | Descripción                                                                         |

|------------------------------------------|-------------------------------------------------------------------------------------|

| Working Voltage                          | Tensión que puede aplicarse continuamente entre entrada y salida                    |

| Isolation Voltage / Withstand<br>Voltage | Tensión de prueba (1 seg – 60 seg) que el optoacoplador puede soportar sin romperse |

Nos fijamos solo en "Isolation Voltage" para el diseño de unas fuentes auxiliares en fotovoltaica y empezaron a romperse después de unos meses.

Hubo que referenciarlas todas al rail de baja tensión, que era la idea inicial, pero no se instalaron correctamente.

El problema es que había unas "miles" instaladas

## No hace falta medir EMI

- Fuentes de alimentación trabajaban correctamente en el laboratorio, no parece haber grandes picos de tensión y se da el funcionamiento por correcto. Trabajarían en una instalación de la que la empresa era propietaria y **se pensó** que no era necesario pasar ningún ensayo de EMC.

- Se construye una planta junto a un Aeropuerto, y el Aeropuerto "**pone una queja**", los aviones pierden la radio.

- Lo hacían unas pequeñas fuentes auxiliares... no los inversores ©

## Maldita estática

Teníamos unos prototipos funcionando y queríamos colocarlos todos sobre un metacrilato.

Con los prototipos **bien cerca**, le quitamos el plástico protector al metacrilato y solo uno de los 8 prototipos que teníamos (trabajaban en serie) volvió a funcionar

# Saber qué les ha pasado a otros nos ayuda a pensar si nos ha pasado lo mismo.

¡Comparte tus errores y ayúdanos a aprender!"

## **Muchas Gracias**

Yann E. Bouvier (URJC)

David Marroquí (UMH)

Miroslav Vasic (UPM)

A. Villarejo (UPCT)